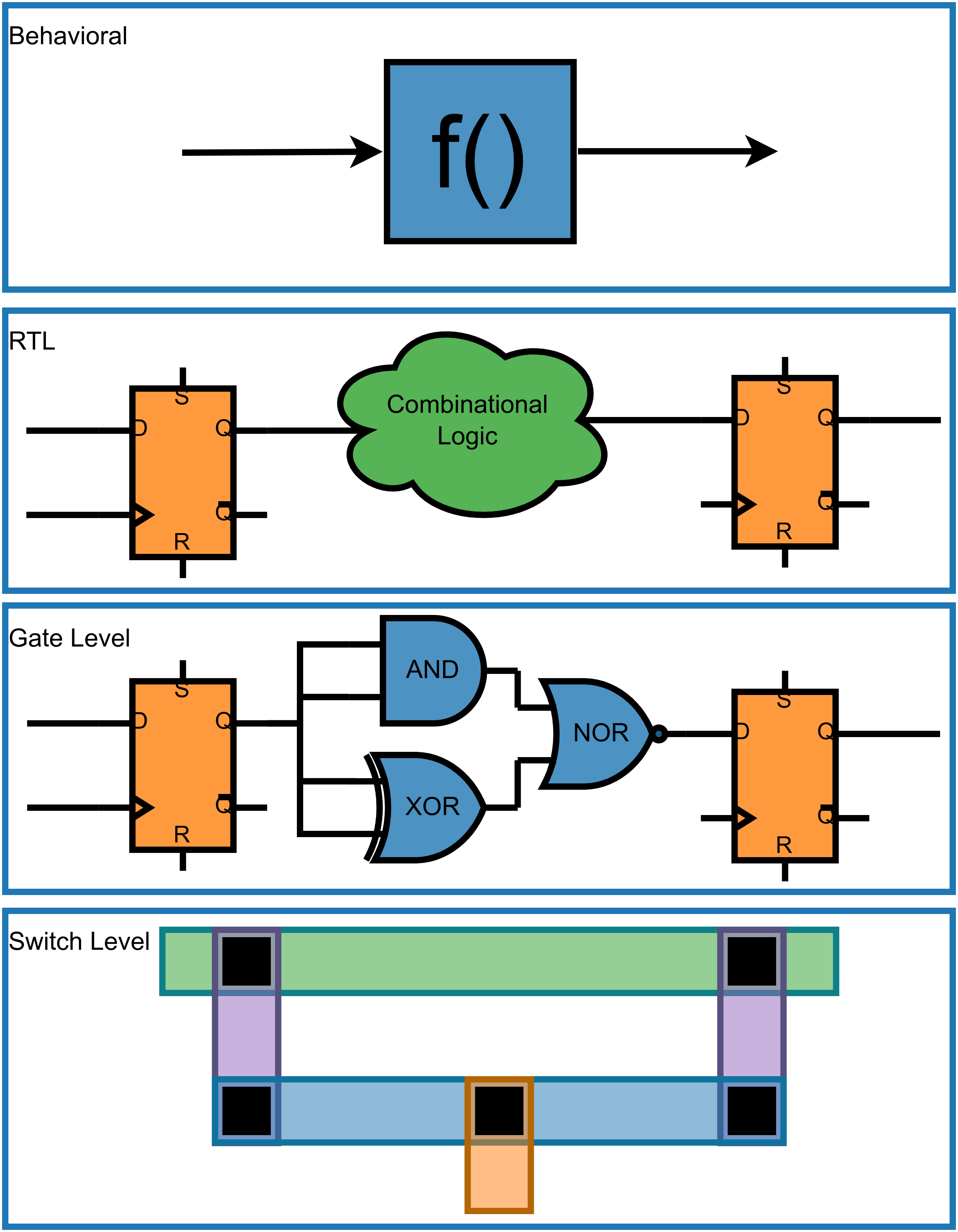

SV1. Levels of Abstraction in Digital Circuit Design

Here’s a quick overview of different levels of abstraction in digital circuit design using SystemVerilog:

Video Tutorial

Watch this comprehensive video explanation of levels of abstraction in digital circuit design:

Algorithmic Level (Digital Design Architect)

- Focuses on functions with an arbitrary number of clock cycles.

- Utilizes algorithms and mathematical equations.

- Can leverage the full capabilities of the SystemVerilog language.

Register Transfer Level (RTL) (Digital Design Engineers)

- Emphasizes functions with specific clock cycle timing.

- Includes combinational and sequential logic.

- Must adhere to strict language constraints to ensure synthesizability.

Gate Level (Standard Cell Library Design Engineer)

- Incorporates both function and structure.

- Utilizes macro cells and logic primitives.

Switch Level (Physical Design Engineers for place and route)

- Closest to the physical silicon implementation.