SystemVerilog

STA

Book Review

SystemVerilog Posts

SV18. A Deep Dive into OBI: Building Your First Master and Slave Controllers

In this tutorial, we'll demystify OBI by designing and verifying a minimal master from the ground up.

SV17. FIFO Design and Implementation

A First-In-First-Out (FIFO) buffer is a fundamental digital design component that stores data in a queue-like structure. This guide provides...

SV16. Finite State Machines (FSM)

Finite State Machines (FSMs) are fundamental building blocks in digital design, providing a structured approach to implementing sequential logic. This...

SV15. SystemVerilog Clock-to-Q Modeling: Why Non-Blocking Assignments Matter

This guide focuses on one of the most important timing parameters: Clock-to-Q delay and how to model it effectively in...

SV14. Unique and Priority Identifiers in SystemVerilog

SystemVerilog provides three special keywords (`unique`, `unique0`, and `priority`) that can be used with `case` and `if` statements to provide...

SV13. SystemVerilog Casting Guide

Casting in SystemVerilog is a powerful mechanism for explicitly converting data between different types, sizes, and sign interpretations. This guide...

SV12. Difference between Bitwise NOT (~) and Logical NOT (!)

When working with Verilog or SystemVerilog, it's crucial to understand the distinction between the bitwise NOT operator (`~`) and the...

SV11. Signed Arithmetic in SystemVerilog

This page summarizes the key rules and pitfalls for synthesizable signed arithmetic in SystemVerilog, focusing on vector size, signed vs....

SV10. User-Defined Packages in SystemVerilog

If you work with SystemVerilog, you know the headaches that can come from improper scope management. In this wiki, I...

SV9. SystemVerilog Packed vs. Unpacked arrays

Ever wondered how packed vs. unpacked arrays really work in SystemVerilog? This article dives into the syntax, memory layout, and...

SV8. SystemVerilog Implicit Net Declaration

Tired of silent bugs caused by undeclared signals in SystemVerilog? This article explains how implicit net declarations work, when they...

SV7. SystemVerilog Built-in Data types: Data Type and Types

It covers the key distinctions between: Nets (representing connections) and Variables (representing storage). 2-state and 4-state data types, and how...

SV6. X Value Bugs in Digital Circuit Design (FPGA/ASIC)

𝗫 can represent an uninitialized state, uncertainty, or a conflict in multiple driver situations. The X value does not physically...

SV5. Simulation Event Scheduling in Verilog/SystemVerilog

Deep dive into simulation event scheduling, delta cycles, and non-blocking assignments. Understand how Verilog simulators handle timing and event ordering...

SV4. Differences between ASIC and FPGA RTL Coding

Master the key differences in RTL coding styles for ASIC and FPGA targets. Learn about timing considerations, resource constraints, and...

SV3. Simulation and Synthesis in Digital Design

Explore the fundamental differences between simulation and synthesis in digital design. Understand how your SystemVerilog code behaves in simulation versus...

SV2. Comparing FPGA and ASIC Design Processes

Learn the key differences between FPGA and ASIC design flows. Understand when to choose each approach and the trade-offs involved...

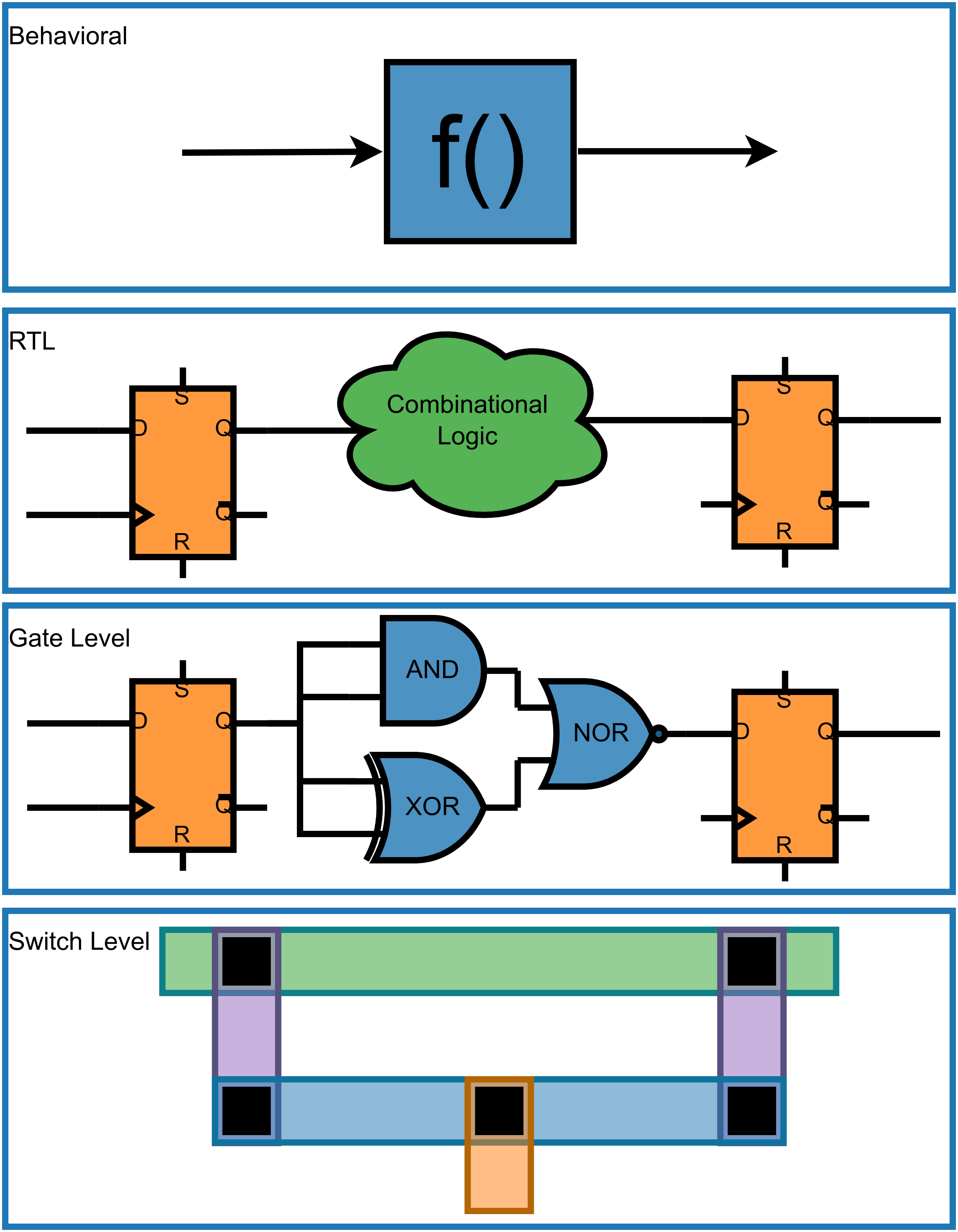

SV1. Levels of Abstraction in Digital Circuit Design

Understanding different levels of abstraction is crucial for effective digital circuit design. Learn about algorithmic, RTL, gate, and switch levels...